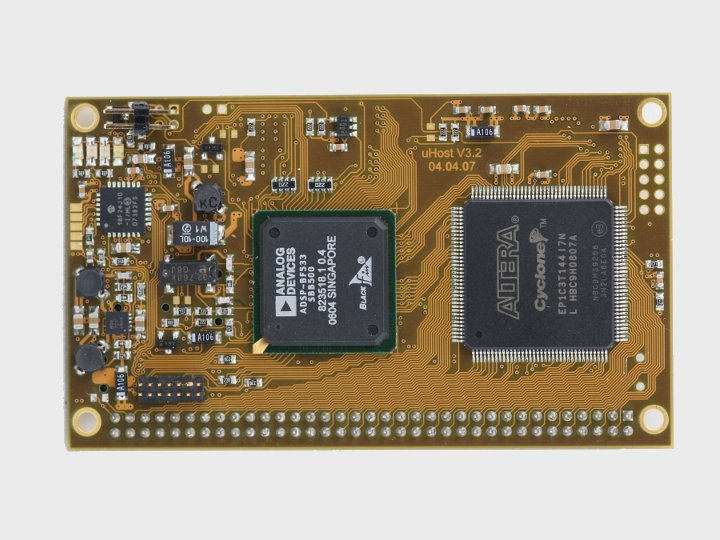

| System | |

|---|---|

| CPU | DSP Analog Devices Blackfin ADSP-BF533 @ 470 MHz |

| RAM | 32 Mbytes SDRAM @ 117 MHz |

| Flash ROM | 4 Mbytes |

| FPGA | Altera FPGA Cyclone EP1C3T144I7 from Intel Corp. |

| JTAG | Analog Devices JTAG connector (not soldered), Altera FPGA JTAG connector for debugging, diagnostics and manufacturing |

| RTC | With connector for external battery, 4 pin connector |

| Microchip PIC | PIC18F24 for power good monitoring and HASP customer options |

| Interfaces | |

| Blackfin on-chip UART, RS-422 | For servicing (user software, FPGA project update) and debugging |

| SPI | 1 interface with 4 chip selects, can be program as GPIO pins, 10 pin connector |

| PPI | 1 interface with 8 bit data bus, can be program as GPIO pins, 14 pin connector |

| SPORT | Dual-channel synchronous serial port, 1 interface, 10 pin connector |

| Expansion connector | For optional interfaces to FPGA, 53 GPIO in 70 pin connector |

| LEDs | 2 user LEDs |

| Power, environmental and mechanical | |

| Power Supply | +5 V, 120… 330 mA (depends on SDRAM and FPGA usage) |

| Temp. range | -40 °C…+85 °C |

| Dimensions | 80 mm x 48 mm x 8 mm |

Versions of delivery:

1. uClinux OS:

- u-boot boot loader;

- uClinux drivers support for module devices;

- demonstration FPGA project written into Flash ROM (with source code).

2. Non-OS:

- boot loader written into Flash ROM;

- demonstration FPGA project written into Flash ROM (with source code);

- PC software under Microsoft Windows for flashing user software and FPGA project via serial RS-422 interface;

- Blackfin software examples with source code.